The rise of thin wafer technology

The transition from planar SoC to 3D-IC and advanced packaging requires thinner wafers to improve performance, reduce power consumption, shorten the distance required for signal transmission, and reduce the energy required for driving signals.

The market for ultra-thin wafers is constantly expanding. The total thickness of an HBM module consisting of 12 DRAM chips and one basic logic chip is still less than the thickness of a native silicon wafer. Thin wafers also play a key role in assembling fan out wafer level packaging and advanced 2.5D and 3D packaging for artificial intelligence applications, which are growing much faster than mainstream ICs. In addition, with the industry's demand for lightweight smartphones, wearable devices, and medical electronic products, it seems that without the ability to reliably process thin silicon wafers, modern microelectronics will be difficult to achieve.

The exposure process of thin silicon via (TSV) is a classic process that requires backside treatment. Rick Reed, Advanced 3D/Technology Director at Amkor Technology, said, "In many current applications, the introduction of silicon vias requires a very controllable thinning process, and due to the almost constant need for backside treatment, this process immediately requires the use of temporary bonding and debonding processes

The first step in any wafer thinning process is to determine the target. If there are so-called blind TSVs on a silicon wafer and you don't understand the depth range of all TSVs in the wafer, it is possible to grind some of them, "Reed explained." Due to the fast diffusion rate of copper in the silicon wafer, it can cause leakage. Moreover, it can also contaminate the grinding wheel, so copper will stick to the subsequent wafers

Several key decisions need to be made during the thinning and processing of thin device wafers. Which temporary bonding adhesive is most compatible with the manufacturing process? Can it fix thin wafers in place during various processes including CMP and high-temperature deposition, and remove them cleanly after processing? Which carrier wafer is most suitable for this application, silicon wafer or glass wafer? Which of the several mainstream debonding processes can effectively remove the adhesive at a reasonable cost after processing?

Despite the protection provided by carrier wafers (also known as processing wafers), ultra-thin wafers are still fragile and fragile. This makes them susceptible to damage, resulting in microcracks and cracks during thinning and subsequent high-temperature processes such as plasma enhanced chemical vapor deposition (PECVD). When ultra-thin wafers undergo photolithography patterning PECVD、 Damage is the biggest threat to yield during reflow, cutting, and debonding (removal of carrier). In addition, other issues may arise due to warping and/or gap formation between wafers.

The edge of the wafer is circular at the slope, but this shape will change after thinning. Therefore, if you grind the device wafer, you usually get a very sharp edge, which is ideally only as thin as an atom, "said Thomas Rapps, product manager at Sus." It is very fragile. Edge fragmentation means that a part of the edge will break, and it may also cause cracks that run through the entire wafer. Therefore, to prevent this from happening, edge cutting is usually performed, which also requires the use of grinding wheels. You need to cut a step at the edge of the wafer, and the depth of this step should be at least the thickness of the final wafer

In addition to addressing critical yield issues, chip manufacturers are also seeking solutions that are suitable for their specific device types, with equipment reliability being the primary requirement. Ian Latchford, Director of Product Marketing at Lam Research, said, "As devices become increasingly complex, applications become more specific. Customers need precision and want repeatable processes every time. They don't want generic solutions, but rather solutions that run the same way every time and have high productivity

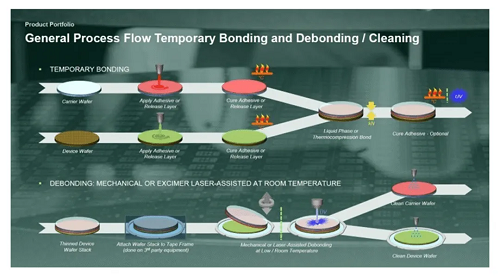

To meet these demands, the industry is improving the thinning steps, chemical composition of adhesives and removers, as well as temporary bonding and debonding processes (see Figure 1). Adhesives are typically organic thermosetting or thermoplastic materials that are coated onto carrier wafers through spin coating, while thinner debonding materials are typically spin coated onto equipment wafers. Bonding is accomplished through vacuum hot pressing (TCB) or through ultraviolet irradiation. The carrier wafer provides the foundation for thinning and processing equipment wafers, until the use of removers during the debonding process.

Figure 1: The process flow of temporary bonding (top) and release bonding (bottom).

Image source: Suss

Silicon and glass carrier wafers

The industry uses both glass carrier wafers and silicon carrier wafers. One of the reasons why glass has become a popular carrier is that its coefficient of thermal expansion (CTE) can be designed to be close to that of silicon, ensuring its compatibility with other materials in the stacked structure. For example, the CTE of borosilicate glass is close to that of silicon, and it is stable over a wide temperature range. It can also allow infrared (IR) or ultraviolet (UV) laser to pass through its surface, thereby activating the release layer of the bond.

Hamed Gholami Derami, Business Development Engineer at Brewer Science, said, "For mechanical and infrared laser bonding, depending on the process requirements, both silicon and glass carriers can be used. However, for ultraviolet laser and photon bonding, glass carriers must be used

Silicon carrier wafers are attractive in part because silicon is compatible with all wafer processing equipment and electrostatic suction cups. The CTE of silicon is perfectly matched with the CTE of silicon devices. The last advantage of silicon is that it can achieve lower TTV (total thickness variation) at a lower cost compared to glass wafers.

The working principle of temporary bonding

When temporarily stacking one wafer onto another, engineers typically use carrier wafers, "glue" or temporary bonding adhesives, and release layers that are easy to remove after processing. In rare cases, a single adhesive layer can accomplish both tasks. Importantly, the bonding and debonding mechanisms work together to ensure that the processed material can be cleanly removed after being released from the carrier.

There are multiple standards to measure the quality of an adhesive. It can achieve bonding at low temperatures while also withstanding high temperature processing. It must be uniformly deposited on a surface of 300 millimeters through spin coating, and a high degree of bonding uniformity must also be achieved.

But a method that is suitable for one application may not be suitable for another application. The main problem is that there is basically no one size fits all solution for all possible process flows, and the most important criterion for material selection is temperature stability. What is the highest temperature in downstream processes between temporary bonding and debonding? Many materials can withstand temperatures up to 250 ℃, because if you perform reflow operations, you usually don't need to exceed this temperature. But only a few materials can withstand high temperatures of 350 ℃

Spin coating provides a certain degree of process flexibility. Rapps said, "By spin coating, you can make the material flat so that it can also embed certain feature structures. Therefore, adhesives have two functions - as adhesives, they can also make the embedded feature structures flat, and the surface morphology of these feature structures may be very low or very high. Therefore, after spin coating, we will bake the wafer and then bond it. And usually this material needs to be cured to stabilize the bonding effect, but it does depend on the specific material solution used

Key points for wafer thinning

Next, the wafer will gradually become thinner. To thin the wafer to below 100 µ m, a delicate balance needs to be achieved between grinding, CMP, and etching processes to meet the strict specifications of TTV, which is the difference between the thickest and thinnest measurements on the wafer. For silicon wafers, laser interferometers are usually used to measure at hundreds of points on the wafer, and TTV is a quality indicator that must be maintained between wafers and batches in large-scale manufacturing.

Thinning wafers is a bit like polishing wood. Start with rough grinding and then use finer sandpaper to achieve the smoothest final result. For wafers, each step can improve the uniformity of wafer indications and reduce TTV.

Matthias Nestler, Director of Product and Technology at Scia Systems, explained, "The roughest method is the wafer grinding step, which results in a final thickness variation range of several micrometers. The CMP step is more precise than wafer grinding, where thickness variation can reach several hundred nanometers. Next, through plasma etching, the thickness variation can reach 10 to 100 nanometers. Alternatively, using ion beam etching as the final step, in the best case scenario, we can reduce the thickness variation of the wafer to one twentieth of its original size, which means that the thickness variation of 250 nanometers can be reduced to 25 nanometers. Moreover, if we adopt a two-step trimming process with a measurement step in between, we can do even better

Given the importance of total thickness variation, engineers are keen to quantify the factors that affect thinning and processing. We use glass carriers in the through silicon via (TSV) exposure process, but even the best glass available has a TTV of only 1 micron on the wafer Amkor's Reed said, "Then, when we apply adhesive on top, this increases the thickness variation by a few micrometers. And then, our grinding process is very uniform, but still introduces about 2 micrometers of TTV

Dry etching can also introduce thickness variations, which may exhibit a radial distribution. So in summary, there will be a thickness variation of about 5 microns, "Reed said.

The key points to ensure precise TSV exposure process include:

Draw the TSV depth determined by Bosch etching method in silicon;

Uniform spin coating of bonding adhesive and release layer, followed by baking, curing, and bonding;

Using rough grinding, medium grinding, and fine grinding methods to grind the silicon backside to within 10 microns from the bottom of the TSV, achieving a mirror effect;

CMP rough grinding, medium grinding, and fine grinding;

Using plasma etching to expose TSV;

Deposition of silicon nitride film as a polishing termination layer;

Deposition of a thick silicon dioxide layer on top of TSV;

Perform CMP again to expose TSV.

Another parameter that needs to be closely monitored is temperature. We are currently in situ controlling the temperature of the CMP process, which overall has many benefits for the CMP process, "said Dan Trojan, CEO of Axus Technology

At present, the most common TSV architecture for silicon intermediate layers may use TSVs with a diameter of 11 microns and a depth of 110 microns, where the barrier metal layer and oxide insulation layer account for 1 micron of the diameter. Although it has been confirmed that TSV with a depth of 55 microns and a diameter of 5 microns can be manufactured, the industry still seems to insist on using thicker and more expensive 100 micron silicon interlayers.

Dealing with defects on the back and edges

The most common problem faced by engineers in thin wafer technology is how to prevent defects or microcracks, especially at the edge of the wafer.

Selective plasma etching performed only at the edge of the wafer helps to remove edge defects, while selective CVD can passivate the edges. In the field of 3D packaging, stacked wafer structures require some material to fill the gaps at the edges, "said Latchford of Lam Research

Plasma etching or ion beam etching processes can also eliminate any defects caused during the CMP process, such as surface scratches, so-called pits (indentations in the silicon lattice), and stains.

Find the correct release method

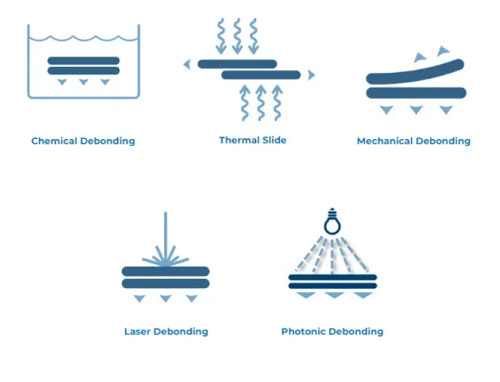

For the debonding process, ultraviolet and infrared laser ablation, as well as photon debonding, have become the main mechanical separation mechanisms because they are compatible with large thin wafer formats (300mm wafers, 50 µ m thick) and can separate wafers with minimal damage to the device compared to thermal sliding and chemical immersion methods (see Figure 2).

Figure 2: The most popular wafer debonding method.

Image source: Brewer Science

Hot sliding debonding uses polymers with lower melting points, namely thermoplastic plastics, which flow when heated to facilitate sliding and separation. Unfortunately, this method is not compatible with thermal processes such as metal PVD or dielectric PECVD, as these thermal processes generate strong stresses that may cause wafer fracture. Hot sliding debonding can also expose the device to unnecessary heat exposure, as other debonding methods can be performed at room temperature. However, thermal sliding debonding is still a low-cost method and a useful choice for smaller and slightly thicker substrates.

The working principle of chemical dissolution is to immerse the bonding pairs in a solvent, and perforated carrier wafers can help accelerate this process. The high solvent consumption and low processing capacity hinder the widespread application of chemical bonding methods.

Photon debonding is a relatively new method of debonding, which uses a pulsed broadband light source to temporarily bond wafer pairs by using a light absorbing layer as an inorganic metal release layer. One advantage of photon debonding is that it has lower cost, faster processing speed, and higher tolerance for changes in the focal length of the release layer compared to laser ablation methods. This makes it suitable for bonding wafer pairs with certain warpage or curvature. For applications where the substrate is thinned to below 20 µ m and very high downstream temperature processes are used (in which control of adhesion and TTV is crucial), photon debonding may be a preferred debonding method.

Mechanical debonding (also known as mechanical stripping) is the process of inserting a blade between a pair of wafers to physically separate them. This method requires the device wafer to withstand a certain physical stress.

Laser ablation uses ultraviolet laser (254, 308, or 355nm) or infrared laser (1064nm), combined with a release layer tuned to the corresponding wavelength, to absorb illumination energy, undergo chemical changes, and achieve separation. It is the fastest de bonding method, capable of processing approximately 20 to 30 wafers per hour with minimal stress on the wafers. However, a shielding layer may be required to reduce any damage caused by laser sound waves to the device.

conclusion

Wafer thinning, temporary bonding, thin wafer processing, and debonding methods are becoming essential process steps in 2.5D and 3D packaging, wafer stacking, and wafer level fanout packaging. Chip manufacturers are working closely with suppliers to select suitable adhesives, release materials, bonding machines, debonding methods, grinding CMP、 Etching and cleaning processes enable the production of ultra-thin devices with a thickness of less than 50 µ m with high yield and reliability. This requires thermal stability, mechanical stability, and attention to wafer edges, all of which are necessary to reduce potential defects and improve yield when using these critical thin wafer processes.